Features

CPU: AM3354

ARCH: Cortex A8

Frequency: 800MHz

Memory: 128Mbyte

Flash: 256Mbyte

Operating System: Linux 3.12.0

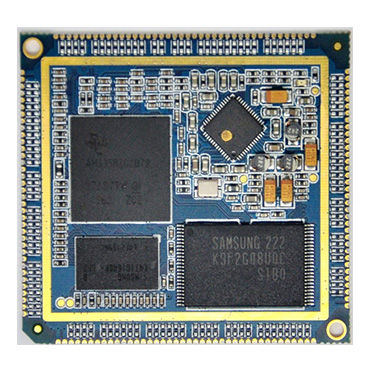

Interface Method: stamp hole

This is a embedded development board with the Ti AM3354 processor as the core. The board is compatible with AM3352 AM3356 AM3358 processor. The AM3354 series processor is based on high-performance ARM Cortex-A8 32-bit RISC as the core, with a maximum operating speed of 1GHz, and providing 3D graphics acceleration. It supports DDR3 DDR3L memory. The PRU-ICSS subsystem provides additional flexibility for the device to meet the industry to meet the industry to meet the industry Design needs.

interface | describe |

CPU | AM3354 |

Operating Temperature | -40℃~+85℃ |

ARCH | ARMv7 Cortex-A8 |

Frequency | 800MHz |

Memory | 128MB DDR |

ROM | 256MB SLC NAND |

Size | 50mm*45mm |

Relative Humidity | 10%~90%(No exposure) |

Operating Voltage | 5V Voltage Supply |

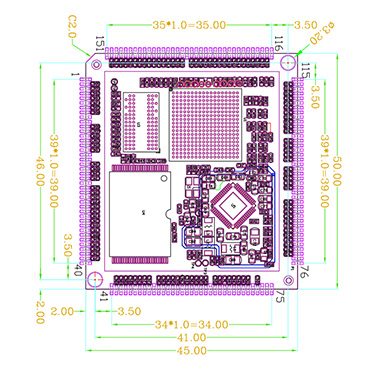

Mechanical Size:

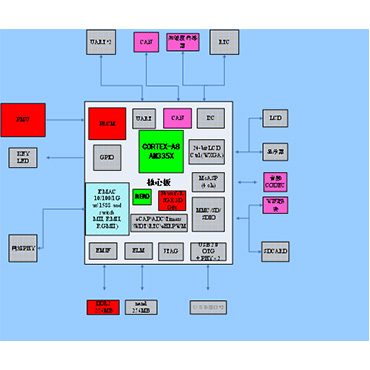

Product Application Function Box Diagram:

Pin Definition:

Pins | Pins | All function or introduction |

1 | GND | Systematically |

2 | MCASP0_AHCLKX | [MCASP0_AHCLKX/EQEP0_STROBE/MCASP0_AXR3/MCASP1_AXR1/EMU4/PR1_PRU0_PRU_R30_7/PR1_PRU0_PRU_R31_7/GPIO3_21] |

3 | MCASP0_FSR | [MCASP0_FSX/EHRPWM0B//SPI1_D0/MMC1_SDCD/PR1_PRU0_PRU_R30_1/PR1_PRU0_PRU_R31_1/GPIO3_15] |

4 | MCASP0_AXR1 | [MCASP0_AXR1/EQEP0_INDEX//MCASP1_AXR0/EMU3/PR1_PRU0_PRU_R30_6/PR1_PRU0_PRU_R31_6/GPIO3_20] |

5 | MCASP0_ACLKX | [MCASP0_ACLKX/EHRPWM0A//SPI1_SCLK/MMC0_SDCD/PR1_PRU0_PRU_R30_0/PR1_PRU0_PRU_R31_0/GPIO3_14] |

6 | MCASP0_FSX | [MCASP0_FSX/EHRPWM0B//SPI1_D0/MMC1_SDCD/PR1_PRU0_PRU_R30_1/PR1_PRU0_PRU_R31_1/GPIO3_15] |

7 | MCASP0_AXR0 | [MCASP0_AXR0/EHRPWM0_TRIPZONE_INPUT//SPI1_D1/MMC2_SDCD/PR1_PRU0_PRU_R30_2/PR1_PRU0_PRU_R31_2/GPIO3_16] |

8 | MCASP0_AHCLKR | [MCASP0_AHCLKR/EHRPWM0_SYNCI/MCASP0_AXR2/SPI1_CS0/ECAP2_IN_PWM2_OUT/PR1_PRU0_PRU_R30_3/PR1_PRU0_PRU_R31_3/GPIO3_17] |

9 | GND | Systematically |

10 | GND | Systematically |

11 | AIN5 | AIN5 |

12 | AIN4 | AIN4 |

13 | TS_AIN3 | AIN3 |

14 | TS_AIN2 | AIN2 |

15 | TS_AIN1 | AIN1 |

16 | TS_AIN0 | AIN0 |

17 | GND | Systematically |

18 | GND | Systematically |

19 | LCD_VSYNC | [LCD_VSYNC/GPMC_A8//PR1_EDIO_DATA_IN2/PR1_EDIO_DATA_OUT2/PR1_PRU1_PRU_R30_8/PR1_PRU1_PRU_R31_8/GPIO2_22] |

20 | LCD_HSYNC | [LCD_HSYNC/GPMC_A9//PR1_EDIO_DATA_IN3/PR1_EDIO_DATA_OUT3/PR1_PRU1_PRU_R30_9/PR1_PRU1_PRU_R31_9/GPIO2_23] |

21 | LCD_AC_BIAS_EN | [LCD_AC_BIAS_EN/GPMC_A11/PR1_MII1_CRS/PR1_EDIO_DATA_IN5/PR1_EDIO_DATA_OUT5/PR1_PRU1_PRU_R30_11/PR1_PRU1_PRU_R31_11/GPIO2_25] |

22 | LCD_PCLK | [LCD_PCLK/GPMC_A10/PR1_MII0_CRS/PR1_EDIO_DATA_IN4/PR1_EDIO_DATA_OUT4/PR1_PRU1_PRU_R30_10/PR1_PRU1_PRU_R31_10/GPIO2_24] |

23 | GND | Systematically |

24 | LCD_DATA0 | [LCD_DATA0/GPMC_A0/PR1_MII_MT0_CLK/EHRPWM2A//PR1_PRU1_PRU_R30_0/PR1_PRU1_PRU_R31_0/GPIO2_6] |

25 | LCD_DATA1 | [LCD_DATA1/GPMC_A1/PR1_MII0_TXEN/EHRPWM2B//PR1_PRU1_PRU_R30_1/PR1_PRU1_PRU_R31_1/GPIO2_7] |

26 | LCD_DATA2 | [LCD_DATA2/GPMC_A2/PR1_MII0_TXD3/EHRPWM2_TRIPZONE_INPUT//PR1_PRU1_PRU_R30_2/PR1_PRU1_PRU_R31_2/GPIO2_8] |

27 | LCD_DATA3 | [LCD_DATA3/GPMC_A3/PR1_MII0_TXD2/EHRPWM0_SYNCO//PR1_PRU1_PRU_R30_3/PR1_PRU1_PRU_R31_3/GPIO2_9] |

28 | LCD_DATA4 | [LCD_DATA4/GPMC_A4/PR1_MII0_TXD1/EQEP2A_IN//PR1_PRU1_PRU_R30_4/PR1_PRU1_PRU_R31_4/GPIO2_10] |

29 | LCD_DATA5 | [LCD_DATA5/GPMC_A5/PR1_MII0_TXD0/EQEP2B_IN//PR1_PRU1_PRU_R30_5/PR1_PRU1_PRU_R31_5/GPIO2_11] |

30 | LCD_DATA6 | [LCD_DATA6/GPMC_A6/PR1_EDIO_DATA_IN6/EQEP2_INDEX/PR1_EDIO_DATA_OUT6/PR1_PRU1_PRU_R30_6/PR1_PRU1_PRU_R31_6/GPIO2_12] |

31 | LCD_DATA7 | [LCD_DATA7/GPMC_A7/PR1_EDIO_DATA_IN7/EQEP2_STROBE/PR1_EDIO_DATA_OUT7/PR1_PRU1_PRU_R30_7/PR1_PRU1_PRU_R31_7/GPIO2_13] |

32 | LCD_DATA8 | [LCD_DATA8/GPMC_A12/EHRPWM1_TRIPZONE_INPUT/MCASP0_ACLKX/UART5_TXD/PR1_MII0_RXD3/UART2_CTSN/GPIO2_14] |

33 | LCD_DATA9 | [LCD_DATA9/GPMC_A13/EHRPWM0_SYNCO/MCASP0_FSX/UART5_RXD/PR1_MII0_RXD2/UART2_RTSN/GPIO2_15] |

34 | LCD_DATA10 | [LCD_DATA10/GPMC_A14/EHRPWM1A/MCASP0_AXR0//PR1_MII0_RXD1/UART3_CTSN/GPIO2_16] |

35 | LCD_DATA11 | [LCD_DATA11/GPMC_A15/EHRPWM1B/MCASP0_AHCLKR/MCASP0_AXR2/PR1_MII0_RXD0/UART3_RTSN/GPIO2_17] |

36 | LCD_DATA12 | [LCD_DATA12/GPMC_A16/EQEP1A_IN/MCASP0_ACLKR/MCASP0_AXR2/PR1_MII0_RXLINK/UART4_CTSN/GPIO0_8] |

37 | LCD_DATA13 | [LCD_DATA13/GPMC_A17/EQEP1B_IN/MCASP0_FSR/MCASP0_AXR3/PR1_MII0_RXER/UART4_RTSN/GPIO0_9] |

38 | LCD_DATA14 | [LCD_DATA14/GPMC_A18/EQEP1_INDEX/MCASP0_AXR1/UART5_RXD/PR1_MII_MR0_CLK/UART5_CTSN/GPIO0_10] |

39 | LCD_DATA15 | [LCD_DATA15/GPMC_A19/EQEP1_STROBE/MCASP0_AHCLKX/MCASP0_AXR3/PR1_MII0_RXDV/UART5_RTSN/GPIO0_11] |

40 | GND | Systematically |

41 | GND | Systematically |

42 | GPMC_AD15 | [GPMC_AD15/LCD_DATA16/MMC1_DAT7/MMC2_DAT3/EQEP2_STROBE/PR1_ECAP0_ECAP_CAPIN_APWM_O/PR1_PRU0_PRU_R31_15/GPIO1_15] |

43 | GPMC_AD14 | [GPMC_AD14/LCD_DATA17/MMC1_DAT6/MMC2_DAT2/EQEP2_INDEX/PR1_MII0_TXD0/PR1_PRU0_PRU_R31_14/GPIO1_14] |

44 | GPMC_AD13 | [GPMC_AD13/LCD_DATA18/MMC1_DAT5/MMC2_DAT1/EQEP2B_IN/PR1_MII0_TXD1/PR1_PRU0_PRU_R30_15/GPIO1_13] |

45 | GPMC_AD12 | [GPMC_AD12/LCD_DATA19/MMC1_DAT4/MMC2_DAT0/EQEP2A_IN/PR1_MII0_TXD2/PR1_PRU0_PRU_R30_14/GPIO1_12] |

46 | GPMC_AD11 | [GPMC_AD11/LCD_DATA20/MMC1_DAT3/MMC2_DAT7/EHRPWM0_SYNCO/PR1_MII0_TXD3//GPIO0_27] |

47 | GPMC_AD10 | [GPMC_AD10/LCD_DATA21/MMC1_DAT2/MMC2_DAT6/EHRPWM2_TRIPZONE_INPUT/PR1_MII0_TXEN//GPIO0_26] |

48 | GPMC_AD9 | [GPMC_AD9/LCD_DATA22/MMC1_DAT1/MMC2_DAT5/EHRPWM2B/PR1_MII0_COL//GPIO0_23] |

49 | GPMC_AD8 | [GPMC_AD8/LCD_DATA23/MMC1_DAT0/MMC2_DAT4/EHRPWM2A/PR1_MII_MT0_CLK//GPIO0_22] |

50 | GND | Systematically |

51 | I2C0_SDA | [I2C0_SDA/TIMER4/UART2_CTSN/ECAP2_IN_PWM2_OUT////GPIO3_5] |

52 | I2C0_SCL | [I2C0_SCL/TIMER7/UART2_RTSN/ECAP1_IN_PWM1_OUT////GPIO3_6] |

53 | GPMC_OEn_REn | [GPMC_OEN_REN//TIMER7/////GPIO2_3] |

54 | GPMC_AD7 | [GPMC_AD7/MMC1_DAT7//////GPIO1_7] |

55 | GPMC_AD6 | [GPMC_AD6/MMC1_DAT6//////GPIO1_6] |

56 | GPMC_AD5 | [GPMC_AD5/MMC1_DAT5//////GPIO1_5] |

57 | GPMC_AD4 | [GPMC_AD4/MMC1_DAT4//////GPIO1_4] |

58 | GPMC_AD3 | [GPMC_AD3/MMC1_DAT3//////GPIO1_3] |

59 | GPMC_AD2 | [GPMC_AD2/MMC1_DAT2//////GPIO1_2] |

60 | GPMC_AD1 | [GPMC_AD1/MMC1_DAT1//////GPIO1_1] |

61 | GPMC_AD0 | [GPMC_AD0/MMC1_DAT0//////GPIO1_0] |

62 | GND | Systematically |

63 | GPMC_WPn | [GPMC_WPN/GMII2_RXERR/GPMC_CSN5/RMII2_RXERR/MMC2_SDCD/PR1_MII1_TXEN/UART4_TXD/GPIO0_31] |

64 | GPMC_BEn1 | [GPMC_BE1N/GMII2_COL/GPMC_CSN6/MMC2_DAT3/GPMC_DIR/PR1_MII1_RXLINK/MCASP0_ACLKR/GPIO1_28] |

65 | GPMC_BE0n_CLE | [GPMC_BE0N_CLE//TIMER5/////GPIO2_5] |

66 | GPMC_ADVn_ALE | [GPMC_ADVN_ALE//TIMER4/////GPIO2_2] |

67 | GPMC_WEn | [GPMC_WEN//TIMER6/////GPIO2_4] |

68 | GPMC_CSn3 | [GPMC_CSN3///MMC2_CMD/PR1_MII0_CRS/PR1_MDIO_DATA/EMU4/GPIO2_0] |

69 | GPMC_CSn2 | [GPMC_CSN2/GPMC_BE1N/MMC1_CMD/PR1_EDIO_DATA_IN7/PR1_EDIO_DATA_OUT7/PR1_PRU1_PRU_R30_13/PR1_PRU1_PRU_R31_13/GPIO1_31] |

70 | GPMC_CSn1 | [GPMC_CSN1/GPMC_CLK/MMC1_CLK/PR1_EDIO_DATA_IN6/PR1_EDIO_DATA_OUT6/PR1_PRU1_PRU_R30_12/PR1_PRU1_PRU_R31_12/GPIO1_30] |

71 | GND | Systematically |

72 | GPMC_CLK | [GPMC_CLK/LCD_MEMORY_CLK/GPMC_WAIT1/MMC2_CLK/PR1_MII1_CRS/PR1_MDIO_MDCLK/MCASP0_FSR/GPIO2_1] |

73 | GND | Systematically |

74 | GND | Systematically |

75 | GND | Systematically |

76 | VBAT | System power input |

77 | VBAT | System power input |

78 | GPMC_A0 | [GPMC_A0/GMII2_TXEN/RGMII2_TCTL/RMII2_TXEN/GPMC_A16/PR1_MII_MT1_CLK/EHRPWM1_TRIPZONE_INPUT/GPIO1_16] |

79 | GPMC_A1 | [GPMC_A1/GMII2_RXDV/RGMII2_RCTL/MMC2_DAT0/GPMC_A17/PR1_MII1_TXD3/EHRPWM0_SYNCO/GPIO1_17] |

80 | GPMC_A2 | [GPMC_A2/GMII2_TXD3/RGMII2_TD3/MMC2_DAT1/GPMC_A18/PR1_MII1_TXD2/EHRPWM1A/GPIO1_18] |

81 | GPMC_A3 | [GPMC_A3/GMII2_TXD2/RGMII2_TD2/MMC2_DAT2/GPMC_A19/PR1_MII1_TXD1/EHRPWM1B/GPIO1_19] |

82 | GPMC_A4 | [GPMC_A4/GMII2_TXD1/RGMII2_TD1/RMII2_TXD1/GPMC_A20/PR1_MII1_TXD0/EQEP1A_IN/GPIO1_20] |

83 | GPMC_A5 | [GPMC_A5/GMII2_TXD0/RGMII2_TD0/RMII2_TXD0/GPMC_A21/PR1_MII1_RXD3/EQEP1B_IN/GPIO1_21] |

84 | GPMC_A6 | [GPMC_A6/GMII2_TXCLK/RGMII2_TCLK/MMC2_DAT4/GPMC_A22/PR1_MII1_RXD2/EQEP1_INDEX/GPIO1_22] |

85 | GPMC_A7 | [GPMC_A7/GMII2_RXCLK/RGMII2_RCLK/MMC2_DAT5/GPMC_A23/PR1_MII1_RXD1/EQEP1_STROBE/GPIO1_23] |

86 | GPMC_A8 | [GPMC_A8/GMII2_RXD3/RGMII2_RD3/MMC2_DAT6/GPMC_A24/PR1_MII1_RXD0/MCASP0_ACLKX/GPIO1_24] |

87 | GPMC_A9 | [GPMC_A9/GMII2_RXD2/RGMII2_RD2/MMC2_DAT7/GPMC_A25/PR1_MII_MR1_CLK/MCASP0_FSX/GPIO1_25] |

88 | GPMC_A10 | [GPMC_A10/GMII2_RXD1/RGMII2_RD1/RMII2_RXD1/GPMC_A26/PR1_MII1_RXDV/MCASP0_AXR0/GPIO1_26] |

89 | GPMC_A11 | [GPMC_A11/GMII2_RXD0/RGMII2_RD0/RMII2_RXD0/GPMC_A27/PR1_MII1_RXER/MCASP0_AXR1/GPIO1_27] |

90 | GND | Systematically |

91 | GND | Systematically |

92 | USB1_VBUS | USB1_VBUS 仅用于USB功能 |

93 | USB1_DP | USB1_DP 仅用于USB功能 |

94 | USB1_DM | USB1_DM 仅用于USB功能 |

95 | USB1_ID | USB1_ID 仅用于USB功能 |

96 | USB1_DRVVBUS | [USB1_DRVVBUS///////GPIO3_13] |

97 | GND | Systematically |

98 | USB0_VBUS | USB0_VBUS 仅用于USB功能 |

99 | USB0_DP | USB0_DP 仅用于USB功能 |

100 | USB0_DM | USB0_DM 仅用于USB功能 |

101 | USB0_ID | USB0_ID 仅用于USB功能 |

102 | USB0_DRVVBUS | [USB0_DRVVBUS///////GPIO0_18] |

103 | GND | Systematically |

104 | GMII1_MDIO_DATA | [MDIO_DATA/TIMER6/UART5_RXD/UART3_CTSN/MMC0_SDCD/MMC1_CMD/MMC2_CMD/GPIO0_0] |

105 | GMII1_MDIO_CLK | [MDIO_CLK/TIMER5/UART5_TXD/UART3_RTSN/MMC0_SDWP/MMC1_CLK/MMC2_CLK/GPIO0_1] |

106 | GMII1_RXCLK | [GMII1_RXCLK/UART2_TXD/RGMII1_RCLK/MMC0_DAT6/MMC1_DAT1/UART1_DSRN/MCASP0_FSX/GPIO3_10] |

107 | GMII1_RXD3 | [GMII1_RXD3/UART3_RXD/RGMII1_RD3/MMC0_DAT5/MMC1_DAT2/UART1_DTRN/MCASP0_AXR0/GPIO2_18] |

108 | GMII1_RXD2 | [GMII1_RXD2/UART3_TXD/RGMII1_RD2/MMC0_DAT4/MMC1_DAT3/UART1_RIN/MCASP0_AXR1/GPIO2_19] |

109 | GMII1_RXD1 | [GMII1_RXD1/RMII1_RXD1/RGMII1_RD1/MCASP1_AXR3/MCASP1_FSR/EQEP0_STROBE/MMC2_CLK/GPIO2_20] |

110 | GMII1_RXD0 | [GMII1_RXD0/RMII1_RXD0/RGMII1_RD0/MCASP1_AHCLKX/MCASP1_AHCLKR/MCASP1_ACLKR/MCASP0_AXR3/GPIO2_21] |

111 | GMII1_TXD3 | [GMII1_TXD3/DCAN0_TX/RGMII1_TD3/UART4_RXD/MCASP1_FSX/MMC2_DAT1/MCASP0_FSR/GPIO0_16] |

112 | GMII1_TXD2 | [GMII1_TXD2/DCAN0_RX/RGMII1_TD2/UART4_TXD/MCASP1_AXR0/MMC2_DAT2/MCASP0_AHCLKX/GPIO0_17] |

113 | GMII1_TXD1 | [GMII1_TXD1/RMII1_TXD1/RGMII1_TD1/MCASP1_FSR/MCASP1_AXR1/EQEP0A_IN/MMC1_CMD/GPIO0_21] |

114 | GMII1_TXD0 | [GMII1_TXD0/RMII1_TXD0/RGMII1_TD0/MCASP1_AXR2/MCASP1_ACLKR/EQEP0B_IN/MMC1_CLK/GPIO0_28] |

115 | GND | Systematically |

116 | GND | Systematically |

117 | GMII1_TXCLK | [GMII1_TXCLK/UART2_RXD/RGMII1_TCLK/MMC0_DAT7/MMC1_DAT0/UART1_DCDN/MCASP0_ACLKX/GPIO3_9] |

118 | GMII1_RXDV | [GMII1_RXDV/LCD_MEMORY_CLK/RGMII1_RCTL/UART5_TXD/MCASP1_ACLKX/MMC2_DAT0/MCASP0_ACLKR/GPIO3_4] |

119 | GMII1_RXERR | [GMII1_RXERR/RMII1_RXERR/SPI1_D1/I2C1_SCL/MCASP1_FSX/UART5_RTSN/UART2_TXD/GPIO3_2] |

120 | GMII1_TXEN | [GMII1_TXEN/RMII1_TXEN/RGMII1_TCTL/TIMER4/MCASP1_AXR0/EQEP0_INDEX/MMC2_CMD/GPIO3_3] |

121 | GMII1_CRS | [GMII1_CRS/RMII1_CRS_DV/SPI1_D0/I2C1_SDA/MCASP1_ACLKX/UART5_CTSN/UART2_RXD/GPIO3_1] |

122 | MCASP0_ACLKR | [MCASP0_ACLKR/EQEP0A_IN/MCASP0_AXR2/MCASP1_ACLKX/MMC0_SDWP/PR1_PRU0_PRU_R30_4/PR1_PRU0_PRU_R31_4/GPIO3_18] |

123 | SYS_RESETn | [NRESETIN_OUT] 用于复位其余外设 |

124 | NMI | [NNMI] |

125 | PMIC_PWR_EN | PMIC_POWER_EN |

126 | MMC0_DAT3 | [MMC0_DAT3/GPMC_A20/UART4_CTSN/TIMER5/UART1_DCDN/PR1_PRU0_PRU_R30_8/PR1_PRU0_PRU_R31_8/GPIO2_26] |

127 | MMC0_DAT2 | [MMC0_DAT2/GPMC_A21/UART4_RTSN/TIMER6/UART1_DSRN/PR1_PRU0_PRU_R30_9/PR1_PRU0_PRU_R31_9/GPIO2_27] |

128 | MMC0_DAT1 | [MMC0_DAT1/GPMC_A22/UART5_CTSN/UART3_RXD/UART1_DTRN/PR1_PRU0_PRU_R30_10/PR1_PRU0_PRU_R31_10/GPIO2_28] |

129 | MMC0_DAT0 | [MMC0_DAT0/GPMC_A23/UART5_RTSN/UART3_TXD/UART1_RIN/PR1_PRU0_PRU_R30_11/PR1_PRU0_PRU_R31_11/GPIO2_29] |

130 | MMC0_CMD | [MMC0_CMD/GPMC_A25/UART3_RTSN/UART2_TXD/DCAN1_RX/PR1_PRU0_PRU_R30_13/PR1_PRU0_PRU_R31_13/GPIO2_31] |

131 | MMC0_CLK | [MMC0_CLK/GPMC_A24/UART3_CTSN/UART2_RXD/DCAN1_TX/PR1_PRU0_PRU_R30_12/PR1_PRU0_PRU_R31_12/GPIO2_30] |

132 | XDMA_EVENT_INTR1 | [XDMA_EVENT_INTR1//TCLKIN/CLKOUT2/TIMER7/PR1_PRU0_PRU_R31_16/EMU3/GPIO0_20] |

133 | XDMA_EVENT_INTR0 | [XDMA_EVENT_INTR0//TIMER4/CLKOUT1/SPI1_CS1/PR1_PRU1_PRU_R31_16/EMU2/GPIO0_19] |

134 | GND | Systematically |

135 | UART5_TXD | [RMII1_REFCLK/XDMA_EVENT_INTR2/SPI1_CS0/UART5_TXD/MCASP1_AXR3/MMC0_POW/MCASP1_AHCLKX/GPIO0_29] |

136 | UART5_RXD | [GMII1_COL/RMII2_REFCLK/SPI1_SCLK/UART5_RXD/MCASP1_AXR2/MMC2_DAT3/MCASP0_AXR2/GPIO3_0] |

137 | UART4_TXD | [UART0_RTSN/UART4_TXD/DCAN1_RX/I2C1_SCL/SPI1_D1/SPI1_CS0/PR1_EDC_SYNC1_OUT/GPIO1_9] |

138 | UART4_RXD | [UART0_CTSN/UART4_RXD/DCAN1_TX/I2C1_SDA/SPI1_D0/TIMER7/PR1_EDC_SYNC0_OUT/GPIO1_8] |

139 | UART3_TXD | [ECAP0_IN_PWM0_OUT/UART3_TXD/SPI1_CS1/PR1_ECAP0_ECAP_CAPIN_APWM_O/SPI1_SCLK/MMC0_SDWP/XDMA_EVENT_INTR2/GPIO0_7] |

140 | UART3_RXD | [SPI0_CS1/UART3_RXD/ECAP1_IN_PWM1_OUT/MMC0_POW/XDMA_EVENT_INTR2/MMC0_SDCD/EMU4/GPIO0_6] |

141 | DCAN0_TX | [UART1_CTSN/TIMER6/DCAN0_TX/I2C2_SDA/SPI1_CS0/PR1_UART0_CTS_N/PR1_EDC_LATCH0_IN/GPIO0_12] |

142 | DCAN0_RX | [UART1_RTSN/TIMER5/DCAN0_RX/I2C2_SCL/SPI1_CS1/PR1_UART0_RTS_N/PR1_EDC_LATCH1_IN/GPIO0_13] |

143 | UART0_TXD | [UART0_TXD/SPI1_CS1/DCAN0_RX/I2C2_SCL/ECAP1_IN_PWM1_OUT/PR1_PRU1_PRU_R30_15/PR1_PRU1_PRU_R31_15/GPIO1_11] |

144 | UART0_RXD | [UART0_RXD/SPI1_CS0/DCAN0_TX/I2C2_SDA/ECAP2_IN_PWM2_OUT/PR1_PRU1_PRU_R30_14/PR1_PRU1_PRU_R31_14/GPIO1_10] |

145 | UART1_TXD | [UART1_TXD/MMC2_SDWP/DCAN1_RX/I2C1_SCL//PR1_UART0_TXD/PR1_PRU0_PRU_R31_16/GPIO0_15] |

146 | UART1_RXD | [UART1_RXD/MMC1_SDWP/DCAN1_TX/I2C1_SDA//PR1_UART0_RXD/PR1_PRU1_PRU_R31_16/GPIO0_14] |

147 | UART2_RXD | [SPI0_SCLK/UART2_RXD/I2C2_SDA/EHRPWM0A/PR1_UART0_CTS_N/PR1_EDIO_SOF/EMU2/GPIO0_2] |

148 | UART2_TXD | [SPI0_D0/UART2_TXD/I2C2_SCL/EHRPWM0B/PR1_UART0_RTS_N/PR1_EDIO_LATCH_IN/EMU3/GPIO0_3] |

149 | SPI0_D1 | [SPI0_D1/MMC1_SDWP/I2C1_SDA/EHRPWM0_TRIPZONE_INPUT/PR1_UART0_RXD/PR1_EDIO_DATA_IN0/PR1_EDIO_DATA_OUT0/GPIO0_4] |

150 | SPI0_CS0 | [SPI0_CS0/MMC2_SDWP/I2C1_SCL/EHRPWM0_SYNCI/PR1_UART0_TXD/PR1_EDIO_DATA_IN1/PR1_EDIO_DATA_OUT1/GPIO0_5] |

151 | GND | Systematically |

Software Parameter:

U-Boot Version | u-boot-2011.09 | |

Kernel Version | Linux-3.12.10(Complete open source) | |

Burn | SDCard quickly burn | |

Development Environment | Ubuntu10.04 | |

Support Drive | Drive of the network card(pair100M/10M) | RTCReal hour clock DRIVE |

MMCdrive | Audio Drive(IISinterface) | |

LCD RGBdrive | SPIdrive | |

USB2.0interfacedrive | Serial port(Contain6Serial port) | |

PWMDrive (backlight) | USBdrive | |

FlashECCcheck | I2Cdrive | |

NAND Flashdrive | MIPI DSIShow Drive | |

UBIFile system | ADCdrive | |

SDCard Drive | RS485drive | |

LCDFrameBuffer | CANdrive | |

Touch Drive(capacitance) | ||

CPU | TI AM3354 |

Architecture | ARMv7 Cortex-A8 |

2D/3D | support |

Graphic processor | PowerVR SGX530 |

UART | 6road |

LCD | 24bitRGBOutput |

CAN | 2road |

SPI | 2road |

I2C | 3road |

IIS | 2road |

ADC | 8road |

PWM | 3road |

Ethernet | 2roadMAC |

VideoEncoder | Software codec |

SD/MMC/SDIO | 3roadMMCinterface |

USB OTG | 1roadUSB OTG2.0 |

USB Device | 1road USB Device 2.0 |

WTC-3354S:AM3354 800MHZ,128MByte DDR,256MByte NAND